# Scaling of GaSb/InAs Vertical Nanowire Esaki Diodes Down to Sub-10-nm Diameter

Yanjie Shao, Marco G. Pala, David Esseni, Jesus del Alamo

#### ▶ To cite this version:

Yanjie Shao, Marco G. Pala, David Esseni, Jesus del Alamo. Scaling of GaSb/InAs Vertical Nanowire Esaki Diodes Down to Sub-10-nm Diameter. IEEE Transactions on Electron Devices, 2022, 69 (4), pp.2188-2195. 10.1109/TED.2022.3145767. hal-03793957

### HAL Id: hal-03793957 https://cnrs.hal.science/hal-03793957

Submitted on 18 Nov 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Scaling of GaSb/InAs Vertical Nanowire Esaki Diodes Down to Sub-10-nm Diameter

Yanjie Shao, Graduate Student Member, IEEE, Marco Pala, Member, IEEE, David Esseni, Fellow, IEEE and Jesús A. del Alamo, Fellow, IEEE

Abstract—This work studies the diameter scaling behavior of broken-band GaSb/InAs vertical nanowire (VNW) Esaki diodes. A top-down fabrication process involving precise reactive-ion etching and alcohol-based digital etch has yielded devices with a tunneling junction diameter below 10 nm. Clear Esaki peaks are observed with an average peak current density of 1 MA/cm<sup>2</sup> and ideal areal scaling over two orders of magnitude in diameter. In the non-Esaki branch, an average current density of 4 MA/cm<sup>2</sup> is demonstrated at 0.3 V. This suggests a great potential for the broken-band GaSb/InAs system for ultra-low power VNW tunnel FET (TFET) applications. Towards evaluating the ultimate TFET potential of this material system, we have extracted the series resistance of our diodes and developed a model for it. We find that the main contribution to the series resistance comes from the GaSb body. Comparatively, the contact resistance at the top of the VNW has a minor impact in spite of the tiny Ni/InAs contact area. Self-consistent quantum transport simulations based on Non-Equilibrium Green's function formalism are carried out. We simulate two devices with different dimensions, i.e. one with strong quantum confinement and one with bulk-like behavior. Inelastic tunneling due to phonon emission is found to both widen the Esaki peak and to suppress tunneling in the non-Esaki branch.

Index Terms—Esaki diode, Tunnel FETs, Nanowires, Topdown, III-Vs, GaSb, InAs, Digital etch, NEGF, Inelastic tunneling, Electron-phonon scattering, Contact resistance.

#### I. Introduction

In the era of Internet of Things (IoTs), innovations in logic transistor technology that can achieve ultra-low power consumption and high performance are of great interest [1]. The fundamental limit of subthreshold swing (S) in MOSFETs prevents supply voltage ( $V_{\rm dd}$ ) scaling of Si CMOS technology, otherwise, the static power consumption in the off-state increases exponentially [2]. Transistors based on band-to-band tunneling (BTBT), usually referred to as tunnel FETs (TFETs), represent one of the most promising device designs capable of achieving a steep turn-on and therefore reduced power consumption [3].

Low BTBT current due to a wide tunneling barrier is one of the long-lasting problems in TFETs, which hampers their use in high-performance logic applications [4]. Considerable effort has been devoted to boosting BTBT current by careful tunnel junction design, from homojunctions composed of narrow-band materials [5], [6], to heterojunctions with staggered- and broken-band alignment [7], [8]. Among all possible designs, the GaSb/InAs material system offers the greatest potential, thanks to its broken-band alignment and excellent transport properties [9]. In spite of promising simulation results of GaSb/InAs TFETs [10], to date, experimentally demonstrated device performance, especially the drive current, has been disappointing [11]. Subthreshold swings (S) as low as 32 and 42 mV/dec over a small current range have been demonstrated in this material system by different research groups [12], [13]. However, onstate currents have remained well below what is desired [12], [13].

In order to exploit the high-quality GaSb/InAs heterojunction that can be grown through molecular-beam epitaxy (MBE) [14], a vertical device geometry is favored. For future logic nodes, a vertical nanowire (VNW) transistor design with sub-10-nm diameter is demanded [15], since it achieves small footprint and effective electrostatic charge control at the same time [16]. Recent experimental results on GaSb/InGaAsSb/InAs VNW TFETs have shown that an *S* as steep as 35 mV/dec could be maintained as the diameter was scaled down from 20 to 10 nm [17]. However, a ~30x degradation in BTBT current was also observed [17]. Strong quantization and thus a lower BTBT rate as diameter decreased were believed to be the reasons for this [17].

Towards contributing fundamental understanding behind this problem, we have fabricated and studied the scaling behavior of GaSb/InAs VNW Esaki diodes with a tunneling junction diameter down to 9 nm. To date, the smallest GaSb/InAs Esaki diodes that have been reported feature a diameter of 40 nm [18], [19], still far above the sub-10-nm scale of interest.

A preliminary report on our devices was given in [20]. This paper expands on that earlier presentation through a more detailed discussion on device fabrication process and current scaling behavior, as well as by developing a model for device series resistance. Furthermore, we carry out more accurate quantum transport simulations using the real dimensions of the fabricated devices. We also study the scaling of BTBT current by comparing a 11-nm diameter device with a bulk-like counterpart. Section II describes the device structure and process technology.

<sup>&</sup>lt;sup>M</sup>anuscript received xx. xx, xxxx. This research was supported by Intel corporation.

Y. Shao and J. A. del Alamo are with the Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, MA 02139, USA (email: shaoyj@mit.edu).

M. Pala is with the Université Paris-Saclay, CNRS, C2N F-91120 Palaiseau, France.

D. Esseni is with the DPIA, University of Udine, Via delle Scienze 206, 33100 Udine, Italy.

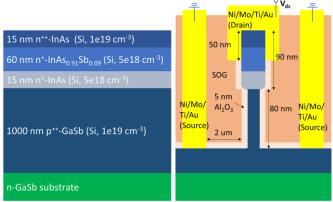

Fig. 1. Schematic cross-sectional diagrams of the starting heterostructure and the finished device.

Section III discusses device electrical characteristics and diameter scaling behavior. In Section IV, we formulate a series resistance model including mushroom top contact resistance, semiconductor resistance, and extrinsic non-scalable resistance. This model is validated by our experimental data. In section V, self-consistent Non-Equilibrium Green's functions (NEGF) simulations are carried out. The influence of inelastic electron-phonon scattering is quantitatively studied.

#### II. DEVICE FABRICATION

Fig. 1 shows schematic cross-sectional diagrams of the starting heterostructure grown by molecular beam epitaxy (MBE) and of a finished device. The heterostructure (described in detail in [20]) is fully-strained. This is expected to result in low defect density within the tunneling junction. We utilize Si as the only dopant throughout the entire heterostructure to achieve an abrupt doping profile at the tunnel junction, since Si is a p-type dopant in GaSb but an n-type dopant in InAs(Sb).

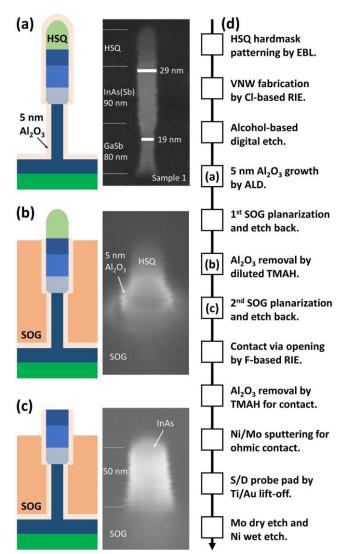

The device fabrication process flow is described in Fig. 2 (d), with schematic cross-sections and scanning electron microscope (SEM) pictures at key steps shown in Figs. 2 (a) to 2 (c). The process starts with electron-beam lithography (EBL) of a hydrogen silsesquioxane (HSQ) hardmask. VNWs are then dry etched using Ar/BCl<sub>3</sub>/SiCl<sub>4</sub> chemistry in an inductively-coupled plasma (ICP) reactive-ion etching (RIE) etcher, following the recipe developed in [21]. A minimum diameter of 23 nm is obtained. Subsequently, 4 cycles of digital etch (DE) with pure oxygen and HCl:IPA are performed [22], [23]. Radial DE rates for GaSb and InAs(Sb) are ~1.7 and ~0.5 nm/cycle, respectively, due to different oxidation rates for the two materials. VNWs with GaSb diameter ( $D_{GaSb}$ ) down to 9 nm are achieved, with the SEM of one of them shown in [20].

Immediately after DE, 5 nm  $Al_2O_3$  is deposited by atomic layer deposition (ALD) for surface passivation. Device fabrication at this stage is illustrated in Fig. 2 (a) in a device with  $D_{GaSb}$  of 9 nm (9 + 2×5 = 19 nm). Spin-on-glass (SOG) is then applied to planarize the VNWs, followed by CF<sub>4</sub> RIE etch back to expose the HSQ mask on top.  $Al_2O_3$  covering the HSQ mask is wet etched by TMAH. Fig. 2 (b) shows the schematic and SEM image at this stage. A second SOG layer is then applied and etched back (together with the HSQ hardmask) to expose the top of the VNWs and create an ohmic contact that extends along the sidewall. This is shown in Fig. 2 (c). Subsequently, a bottom contact via is opened by CF<sub>4</sub> RIE, followed by  $Al_2O_3$  removal,

Fig. 2. Schematics of key processing steps and process flow. Schematics and corresponding SEM images after ALD Al $_2$ O $_3$  growth (a); after 1st SOG planarization, etch back and Al $_2$ O $_3$  removal (b); after 2nd SOG planarization and etch back (c). (d) Process flow for GaSb/lnAs(Sb) VNW Esaki diode fabrication.

Ni/Mo sputtering, and Ti/Au pad lift-off. The device fabrication finishes by Mo dry etch with SF<sub>6</sub>/O<sub>2</sub> RIE and Ni wet etch with Ni etchant using the pads as mask.

The final devices feature single VNWs with  $D_{\rm GaSb}$  ranging from 9 nm to 1000 nm. Two samples (samples 1 and 2) are fabricated at different times through an identical process except that more DE cycles are applied on the latter one. The smallest  $D_{\rm GaSb}$  achieved in sample 2 is 10 nm.

#### III. ELECTRICAL CHARACTERISTICS AND DIAMETER SCALING

We use a TFET-like voltage sign convention ( $V_{\rm ds}$ ) such that a positive  $V_{\rm ds}$  refers to the reverse regime of the p-n junction (n-region positive with respect to p-region). All current density values are calculated with respect to the cross-sectional area of GaSb since that is the narrowest location of the tunnel junction.

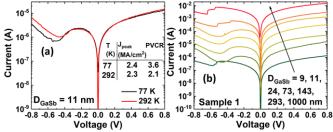

Fig. 3 (a) shows *I-V* characteristics of an exemplar  $D_{\text{GaSb}} = 11$  nm device in log scale. This device exhibits clear negative differential resistance (NDR) with a peak current density ( $J_{\text{peak}}$ ) of 2.3 MA/cm<sup>2</sup> and a peak-to-valley current ratio (PVCR) of 2.1

Fig. 3. (a) I-V characteristics of a  $D_{\text{GaSb}} = 11$  nm device from sample 1 measured at RT and 77 K. Figures of merit are listed in the inset. (b) I-V characteristics at RT for devices from sample 1 with different diameters.

at room temperature (RT). PVCR is found to increase to 3.6 at 77 K with  $J_{\text{peak}}$  unchanged, suggesting the suppression of trapassisted tunneling (TAT) at the Esaki valley [24]. For voltages larger than the Esaki peak voltage ( $|V_{\text{peak}}|$ , the absolute value of  $V_{\text{ds}}$  at which the peak current occurs), we observe temperature-independent characteristics suggesting that pure BTBT is the dominant current mechanism.

Fig. 3 (b) shows *I-V* characteristics of devices with different diameters, from 9 to 1000 nm, at RT.  $|V_{\text{peak}}|$  is independent of diameter except for the narrowest and the widest devices, which both suffer from series resistance (discussed in Sec. IV). In the narrowest device, the excess resistance arises from a non-optimal top contact [20]. For the widest device, it is due to an extrinsic non-scalable resistance that might come from the aggregate of bottom contact, probe pads and probe tips, all estimated to be ~30  $\Omega$ , as we will discuss below.

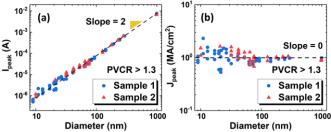

Our Esaki diodes display near-ideal diameter scaling behavior. This is illustrated in Fig. 4 that shows the evolution of Esaki peak current ( $I_{\rm peak}$ ) and peak current density,  $J_{\rm peak}$ , as a function of tunneling junction diameter. We choose devices that exhibit PVCR > 1.3 since  $I_{\rm peak}$  of these devices are minimally affected by the excess valley current. A clear quadratic relationship between  $I_{\rm peak}$  and  $D_{\rm GaSb}$  is demonstrated on these devices over the entire diameter range. An average  $J_{\rm peak}=1$  MA/cm² is achieved.  $I_{\rm peak}$  scaling in both samples 1 and 2 is identical. This is in spite of the fact that VNWs from both samples have a similar  $D_{\rm GaSb}$  of 9 and 10 nm but quite different  $D_{\rm InAs}$  of 19 and 35 nm, respectively (an SEM image of a VNW from sample 2 can be found in [20]). The consistent values of  $J_{\rm peak}$  across both samples confirm that BTBT is limited by the GaSb side of the junction.

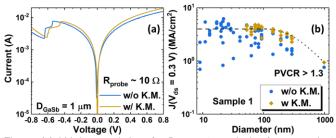

Of greater relevance for ultra-low power GaSb/InAs VNW TFETs is the positive  $V_{\rm ds}$  current branch of our Esaki diodes. In Fig. 3 (a) we observe that it is temperature-independent, consistent with pure BTBT. To quantify our results, we graph in Fig. 5 (b) the current density at  $V_{\rm ds} = 0.3$  V (denoted as  $J(V_{\rm ds} =$ 0.3 V)), as this is the target operating voltage for a future TFET technology [10]. To minimize the impact of non-scalable extrinsic resistance due to probing  $(R_{probe})$ , in wide diameter devices we carry out Kelvin measurements. Fig. 5 (a) shows a  $D_{\text{GaSb}} = 1 \, \mu \text{m}$  device with and without Kelvin probing. From the decrease of  $|V_{peak}|$  after performing the Kelvin measurement and the value of  $I_{\text{peak}}$ , we calculate  $R_{\text{probe}} \sim 10 \Omega$ , which is within the 30  $\Omega$  non-scalable resistance mentioned above. As shown in Fig. 5 (b), ideal scaling of  $J(V_{ds} = 0.3 \text{ V})$  is observed across most of the diameter range, with an average value of 4 MA/cm<sup>2</sup> demonstrated. For large-diameter devices, the current level is

Fig. 4. Diameter scaling of peak current (a) and peak current density (b) of devices with PVCR > 1.3 from samples 1 and 2.

Fig. 5. (a) *I-V* characteristics of a  $D_{\text{GaSb}} = 1$  µm device from sample 1 with and without Kelvin measurement (K.M.). (b) Diameter scaling of current density at 0.3 V of devices with PVCR > 1.3 from sample 1.

also large and the voltage drop on the extrinsic resistance becomes significant even in a Kelvin configuration. We estimate a similar value of the resistance base on the  $J(V_{\rm ds}=0.3~{\rm V})$  drop on large-diameter devices.

#### IV. SERIES RESISTANCE MEASUREMENTS AND MODEL

The series resistance,  $R_s$ , plays a key role in limiting the current of VNW devices. Towards evaluating this, we have extracted  $R_s$  of our diodes from their forward I-V characteristics passed the Esaki peak ( $|V_{ds}| > |V_{peak}|$ ). We can derive  $R_s$  starting from the I-V characteristics of a p-n junction in the forward regime at a  $|V_{ds}|$  greater than several  $k_BT/q$  [25]:

gime at a

$$|V_{ds}|$$

greater than several  $k_BT/q$  [25]:

$$I \approx I_s \exp \frac{q(|V_{ds}| - IR_s)}{nk_BT}$$

(1)

where  $I_s$  is the saturation current, n is the ideality factor, and the rest of the symbols have their usual meanings. From (1) and after some straightforward math, we derive a simple expression for the differential resistance, r:

$$r = \frac{d|V_{ds}|}{dI} = R_s + \frac{nk_BT}{qI} \tag{2}$$

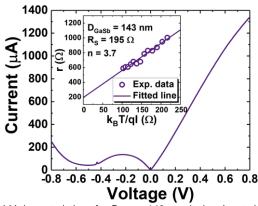

Equation (2) suggests a direct way to estimate  $R_s$  in our devices: a linear regression of r versus  $k_BT/qI$  on the high negative  $V_{\rm ds}$  regime where the carrier transport can be described by (1). We obtain good fittings on almost all devices if we choose the fitting range to start from  $|V_{\rm ds}|=0.7$  V till the highest value that we measure (typically 0.8 V).  $R_s$  in large-diameter devices is generally limited by extrinsic resistance, as noted above. In these cases, the fittings are performed at higher  $|V_{\rm ds}|$  values. An example of the  $R_s$  extraction process is shown in the inset of Fig. 6 for a 143-nm diameter device. The I-V characteristics of the same device are also shown. Using the above procedures, we extract  $R_s$  versus  $D_{\rm GaSb}$  data with and without Kelvin probing, with the results shown in Fig. 7 (b) (dots), where a scaling behavior of  $R_s \propto D_{\rm GaSb}^{-2}$  is observed on all devices except for the larger diameter ones.

Fig. 6. I-V characteristics of a  $D_{\text{GaSb}} = 143$  nm device. Inset shows the linear regression between differential resistance and  $k_{\text{B}}T/qI$ , through which series resistance and ideality factor are extracted.

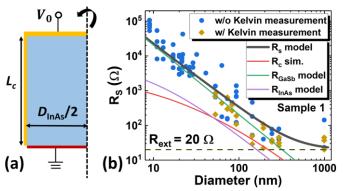

Fig. 7. (a) Radial cross section of the Ni/n<sup>++</sup>-InAs top contact for  $R_c$  TCAD simulations. Yellow and red edges denote the top contact, with an applied voltage of  $V_0$ , and ground, respectively. (b)  $R_s$  *versus* GaSb diameter for extracted  $R_s$  from experimental results from sample 1 (dots) and for modeled  $R_s$  (black line). Different components of  $R_s$  including  $R_c$ ,  $R_{GaSb}$ ,  $R_{InAs}$ , and  $R_{ext}$  are also shown.

We have constructed a model for the series resistance of our devices. To the first order, this can be expressed as:

$$R_s = R_c + R_{\text{InAs}} + R_{\text{GaSb}} + R_{\text{ext}}$$

(3)

Here,  $R_{\rm InAs} = 4\rho_{\rm InAs}(L_{\rm InAs} - L)/\pi D_{\rm InAs}^2$  is the longitudinal resistance of the uncontacted portion of the n<sup>+</sup>-InAs(Sb) region,  $R_{\rm GaSb} = 4\rho_{\rm GaSb}L_{\rm GaSb}/\pi D_{\rm GaSb}^2$  is the longitudinal resistance of the p<sup>+</sup>-GaSb region,  $R_c$  is the n<sup>++</sup>-InAs/Ni top contact resistance, and  $R_{\rm ext} = 20~\Omega$  is the non-scalable resistance (excluding the contact resistance between probe pad and probe tips that can be corrected by Kelvin measurement as shown in Fig. 5 (a)). The bottom contact resistance to p<sup>+</sup>-GaSb is small since the contact area is very large. In addition, this resistance is the same for all the devices we fabricate, so it is part of  $R_{\rm ext}$ .

To calculate  $R_c$ , we carry out simulations in *Synopsys* TCAD *Sentaurus* simulator, in which Poisson equation is solved. A 2D cylindrical coordinate system enables efficient simulations of our radially symmetric 3D structure. The simulation geometry (radial cross section) is shown in Fig. 7 (a), where a NW is contacted from the sidewall (with a length of  $L_c$ ), as well as from the top surface. We extract  $R_c$  for different InAs diameter structures from the slope of the simulated I-V characteristics.

Using (3) and the materials and device parameters of Table I, we can predict  $R_s$  versus  $D_{\text{GaSb}}$ . The specific contact resistance  $(\rho_c)$  for the Ni/n<sup>++</sup>-InAs ohmic contact is adopted from [26] at  $N_{\text{D}} = 10^{19}$  cm<sup>-3</sup>,  $\rho_{\text{GaSb}}$  is calculated using the formula given in

TABLE I

PARAMETERS FOR SERIES RESISTANCE MODELLING

| $\rho_c  (\Omega.\mathrm{cm}^2)$ | $\rho_{\mathrm{InAs}}\left(\Omega.\mathrm{cm}\right)$ | $\rho_{\rm GaSb}(\Omega.{\rm cm})$ | $L_{\mathrm{InAs}}$ (nm) | $L_{\mathrm{GaSb}}$ (nm) | $L_c$ (nm) |

|----------------------------------|-------------------------------------------------------|------------------------------------|--------------------------|--------------------------|------------|

| 10-8                             | 7×10 <sup>-4</sup>                                    | 2×10 <sup>-3</sup>                 | 90                       | 80                       | 25         |

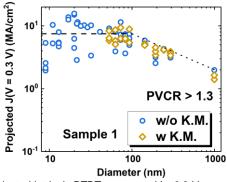

Fig. 8. Projected intrinsic BTBT current at V = 0.3 V versus GaSb diameter for sample 1 after correcting for series resistance. Only devices with PVCR > 1.3 are included. K.M. refers to Kelvin measurements.

[27] at a doping level  $N_{\rm A}=10^{19}~{\rm cm^{-3}}$ , and  $\rho_{\rm InAs}$  is adopted from [28] at a doping level  $N_{\rm D}\approx 6\times 10^{18}~{\rm cm^{-3}}$ , which is similar to the nominal doping level of the n<sup>+</sup>-InAs(Sb) portion of our devices. We adopt  $L_c=25~{\rm nm}$  since Al<sub>2</sub>O<sub>3</sub> is removed only from the top 25 nm of the VNW, as observed in an SEM measurement right before contact metal sputtering.

Fig. 7 (b) shows the modeled  $R_s$  (black line) from (3) as a function of  $D_{GaSb}$ . Excellent agreement is obtained with the experiments, verifying the validity of the assumptions behind our model. If we look at the components of  $R_s$ ,  $R_{GaSb}$  (green line) is found to contribute the most, over most of the diameter range, while the contribution of  $R_c$  (red line) is insignificant in all cases. This model explains the observed scaling behavior of  $R_s$  $\propto D_{\text{GaSb}}^{-2}$  on sub-200-nm diameter devices. This is further indication of the near-ideal nature of our devices. Our model also suggests that  $R_{InAs}$  (purple line) is around one order of magnitude smaller than  $R_{GaSb}$ . This is understandable since the InAs portion of our diodes has a larger diameter and a higher majority carrier mobility than the GaSb portion.  $R_s$  of large diameter devices eventually saturates at 20  $\Omega$ , the value of the extrinsic resistance. Interestingly,  $R_s$  of the  $D_{GaSb} = 9$  nm devices somehow deviates from the model, which might result from a non-ideal top contact as discussed in Section III. An increased  $\rho_c$  value of  $4\times10^{-7}$   $\Omega$ .cm<sup>2</sup> could explain this observation.

Knowing  $R_s$  allows us to project the intrinsic BTBT current density at V = 0.3 V by subtracting the voltage drop on the extracted  $R_s$ . This is of relevance for TFET operation of this layer structure. An average projected J(V = 0.3 V) of 7.5 MA/cm<sup>2</sup> is obtained for sub-100-nm diameter devices, as shown in Fig. 8. As expected, we do not see any difference with or without Kelvin probing. A degraded current density is found for wider devices. A possible reason for this is that there might be some residual resistance that we do not fully correct for. Interestingly, detailed simulations (Section V) for different device diameters also suggest this behavior. Nevertheless, this exercise shows the great potential for high drive current of scaled GaSb/InAs VNW TFETs with optimized geometry.

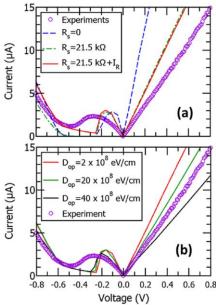

Fig. 9. Simulated (lines) and experimental (symbols) *I-V* curves for the  $D_{\text{GaSb}} = 11$  nm device. (a) Simulations with and without experimentally estimated  $R_{\text{s}}$  and fitted  $I_{R}$ . (b) Simulations including  $R_{\text{s}}$ ,  $I_{R}$  as in (a) and inelastic polar optical phonon scattering for different deformation potential ( $D_{\text{op}}$ ) values.

#### V. QUANTUM TRANSPORT SIMULATIONS

In order to support the interpretation of our experiments, we have performed self-consistent simulations within the Non-Equilibrium Green's functions (NEGF) formalism and adopt an 8×8 k·p Hamiltonian to describe the materials properties [29]. Heterojunctions are described in the real-space Hamiltonian by means of position-dependent k·p parameters [30], and particularly by using the material parameters given in [31]. Tensile strain in the InAs and InAsSb layers induced by lattice mismatch with GaSb is accounted for by employing the strain interaction matrix discussed in [29], and with deformation potentials from [31]. Band gap narrowing due to the high doping concentrations in GaSb and InAs(Sb) is also included according to the experimental values reported in [32], [33].

The simulated devices have a length of the GaSb, InAs, and InAsSb regions equal to the features of the measured samples sketched in Fig.1 (see also the *x*-axis in Figs.10 and 11, where the direction of *x*-axis is the longitudinal transport direction). The numerical burden implied by 3D quantum simulations of such relatively long and wide device structures has been softened by adopting the coupled mode-space approach [31], [34]. We typically use 50 modes for the valence band (VB) of GaSb and 30 modes for the conduction band (CB) of InAs(Sb). Inelastic phonon scattering is also included by using a local formulation for the phonon self-energies, and within the self-consistent Born approximation [34]. We treat acoustic phonons in the elastic approximation, and polar phonons as dispersion-less optical phonons with a phonon energy  $\hbar\omega = 30$  meV.

Figure 9 (a) compares the simulated (lines) and measured (symbols) I-V characteristics of a device with  $D_{GaSb} = 11$  nm and  $D_{InAs} = 21$  nm, where simulations do not account for phonon scattering. The agreement with experiments is improved both at positive and negative  $V_{ds}$  regimes by including the influence of a series resistance  $R_s = 21.5 \text{ k}\Omega$ , whose value is in-

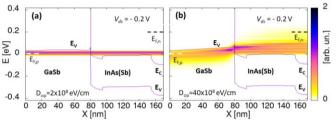

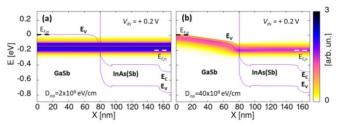

Fig. 10. Current spectra for the simulations in Fig. 9 (b) at  $V_{\rm ds} = -0.2$  V. (a):  $D_{\rm op} = 2 \times 10^8$  eV/cm and (b):  $D_{\rm op} = 40 \times 10^8$  eV/cm. The energy reference is the Fermi level ( $E_{\rm t,p}$ ) in GaSb, so that  $E_{\rm t,n}$  on the InAs side is given by  $-qV_{\rm ds}$ . The lines refer to the spatial profiles of the highest valence subband ( $E_{\rm v}$ ) and of the lowest conduction subband ( $E_{\rm c}$ ).

Fig. 11. Current spectra as in Fig. 10 but here for  $V_{ds} = +0.2 \text{ V}$ .

ferred from Fig. 7 (b) for a GaSb diameter of 11 nm. The simulated valley current tends to largely underestimate experiments, which may be due to the fact that simulations do not include any TAT mechanism [24]. In Fig. 9, we have tried to improve this aspect by introducing a simple, phenomenological model for a non-ideal recombination current, which has the form  $I_R = I_{R0} \left[ \exp \left[ \frac{q|V_{ds}|}{n_R k_B T} \right] - 1 \right]$  in the space charge region, where the pre-factor  $I_{R0}$  has been adjusted to approximately reproduce the Esaki valley current. Still the simulations in Fig. 9 (a) exhibit, compared to experiments, a larger current for positive  $V_{\rm ds}$  regime and a narrower NDR region with a lower  $|V_{\rm peak}|$ .

Fig. 9 (b) shows that the inclusion of phonon scattering improves both aspects above. In fact, Fig. 10 shows that for  $V_{\rm ds}$  = -0.2 V, phonon emission opens an inelastic tunneling path at the tunneling junction located approximately at x=80 nm, which tends to push  $|V_{\rm peak}|$  higher in the NDR region. For  $V_{\rm ds}=+0.2$  V, instead, Fig. 11 reveals that phonons essentially act as a diffusive scattering mechanism that degrades BTBT current. This is particularly clear in the narrower and therefore more resistive quasi-neutral GaSb region, where the resistive voltage drop is not negligible. In both Fig. 10 and Fig. 11 the effect of phonons is much weaker in plots (a) compared to plots (b), because of the corresponding smaller deformation potential,  $D_{\rm op}$ .

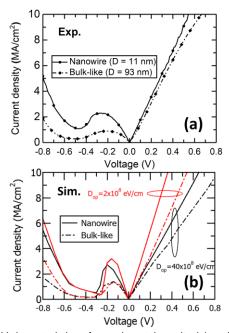

The last simulation-based analysis is devoted to a better understanding of the diameter scaling behavior of  $J_{\rm peak}$ , as shown in Fig. 4. In order to approximate a bulk-like device by using our numerical simulation approach, we have used a large diameter and then employed periodic boundary conditions for the discretization of the  $8\times8$  k·p Hamiltonian at the perimeter of the simulation domain according to the method presented in [35]. We have verified that periodic boundary conditions ensure that the current per unit area in the device is independent of the actual diameter used in simulations when the diameter is larger than ~20 nm. Such periodic boundary conditions effectively suppress any size-induced quantization effects. A sizeable bandgap widening in GaSb region is instead observed in the

Fig. 12. J-V characteristics of experimental results (a) and simulation results (b) for a  $D_{\text{GaSb}} = 11$  nm device and a bulk-like device. Current density is normalized with respect to the cross-sectional area of GaSb. Two values of deformation potential are compared in the simulations for both devices.

$D_{GaSb} = 11 \text{ nm NW (not shown)}$ , where closed boundary conditions have been employed at the perimeter of the device cross section.

In Fig. 12, simulations confirm the experimental observation that the current density in the  $D_{\rm GaSb}=11$  nm device does not degrade with respect to large diameter devices, but actually is enhanced. Within the inevitable scattering in the measured  $J_{\rm peak}$  values reported in Fig. 4 (b), a larger average  $J_{\rm peak}$  in narrow nanowires (compared to bulk-like devices) is also observed even in experiments for diameters between 10 and 20 nm. Hence both experiments and simulations suggest that size-induced quantization does not induce a degradation of the current density in the VNW GaSb/InAs Esaki diodes studied in this work.

#### VI. DISCUSSION

A detailed benchmarking of our devices against the state-ofthe-art can be found in [20]. Our devices achieve the best performance at our nominal doping level with a diameter that is reduced by a factor of >4 below that of any prior device.

In order to understand the excellent results demonstrated in this work, we summarize the following five criteria for designing and fabricating GaSb/InAs Esaki diodes with high BTBT current. These arguments also apply to the design of TFETs in this materials system.

(1) High doping level, especially in the p-GaSb region. High doping levels enhance BTBT due to shorter tunneling paths and more available states to tunnel from and to tunnel into. The valence band effective density of states (N<sub>ν</sub>) of GaSb has a value of 1.8×10<sup>19</sup> cm<sup>-3</sup> [31], which is much larger than the conduction band effective density of states (N<sub>c</sub>) of InAs with a value of 8.7×10<sup>16</sup> cm<sup>-3</sup> [31]. To achieve degenerate doping in p-GaSb, a doping level on the order

of  $10^{19}$  cm<sup>-3</sup> is needed. On the other hand, the doping level in n-InAs is not as critical. In our work, we choose a value of  $5\times10^{18}$  cm<sup>-3</sup>. A way to compare the tunneling performance of different devices with different combinations of doping levels is to define an effective doping level,  $N_{\rm eff} = N_{\rm A}N_{\rm D}/(N_{\rm A}+N_{\rm D})$ , based on  $N_{\rm A}$  in p-GaSb region and  $N_{\rm D}$  in n-InAs region. When done in this way, for equivalent  $N_{\rm eff}$ , our devices perform as good as the best in the literature [20].

- (2) Abrupt composition transition from GaSb to InAs enabled by MBE. This is critical for achieving a desired band alignment, in our case, a broken-band configuration. If the transition is graded, as is the case in MOCVD grown structures, the band alignment becomes staggered-band, and the tunneling path gets significantly longer. To date, only MBE growth can achieve an abruptness within several atomic layers and a high tunneling rate, as demonstrated in the literature [20].

- (3) Abrupt doping type transition from p-GaSb to n-InAs enabled by Si doping. This is also to minimize doping gradients and shorten the tunneling path. Even with the commonly-used *in-situ* doping during MBE growth, the doping gradient at the junction can be on the order of 5 nm/dec. Therefore, using Si on both sides of the tunneling junction minimizes the grading of the transition to within a few atomic layers.

- (4) Lattice-matched substrate and heterojunction. A heterostructure closely lattice-matched to the substrate can be fully strained and therefore include a minimum density of threading dislocations that might originate from epitaxy layer relaxation. Low interface trap density at the junction is key to large PVCR of an Esaki diode, due to low TAT rate. In our design, by including Sb into n<sup>+</sup>-InAs layer, a lattice constant identical to that of GaSb can be maintained, making the heterostructure fully strained [36].

- (5) Critical dimension smaller than 100 nm. As we have shown, a device with a diameter larger than 100 nm suffers from extrinsic resistance that limits its performance at positive V<sub>ds</sub> regime. As a result, scaling down the device dimension is highly favorable.

#### VII. CONCLUSIONS

We present a detailed study of scaling behavior of VNW GaSb/InAs Esaki diodes. These devices exhibit ideal current scaling over two orders of magnitude of diameter, from sub-10 nm to 1  $\mu$ m. We model the total series resistance in our devices based on merely material- and device-related parameters and find that it is dominated by the resistance of the GaSb portion of the diode. Quantum transport simulations show that device characteristics, especially the positive  $V_{\rm ds}$  branch, can be reproduced by adding the inelastic electron-phonon scattering mechanism. Our results clearly demonstrate a high drive current potential of ultra-scaled VNW GaSb/InAs TFETs for future VLSI applications. They also suggest several reasons for the long-lasting mismatch between III-V TFET modeling and experimental demonstrations.

#### ACKNOWLEDGEMENT

Device fabrication was carried out at MIT.nano, MTL,

and SEBL of MIT. We thank Gilbert Dewey, Uygar E. Avci and Ashish V. Penumatcha at Intel Corporation for fruitful discussions. We thank Michael Robinson at Intel Corporation for SIMS measurements.

#### REFERENCES

- A. Steegen, "Technology innovation in an IoT Era," in *Proc. IEEE Symp. VLSI Circuits*, Kyoto, Japan, Jun. 2015, pp. C170-C171, DOI: 10.1109/VLSIC.2015.7231370.

- [2] K. Bernstein, R. K. Cavin, W. Porod, A. Seabaugh and J. Welser, "Device and Architecture Outlook for Beyond CMOS Switches," *Proc. IEEE*, vol. 98, no. 12, pp. 2169-2184, Dec. 2010, DOI: 10.1109/JPROC.2010.2066530.

- [3] A. C. Seabaugh and Q. Zhang, "Low-Voltage Tunnel Transistors for Beyond CMOS Logic," *Proc. IEEE*, vol. 98, no. 12, pp. 2095-2110, Dec. 2010, DOI: 10.1109/JPROC.2010.2070470.

- [4] R. Pandey, S. Mookerjea and S. Datta, "Opportunities and Challenges of Tunnel FETs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 12, pp. 2128-2138, Dec. 2016, DOI: 10.1109/TCSI.2016.2614698.

- [5] M. Luisier and G. Klimeck, "Atomistic Full-Band Design Study of InAs Band-to-Band Tunneling Field-Effect Transistors," *IEEE Electron Device Lett.*, vol. 30, no. 6, pp. 602-604, Jun. 2009, DOI: 10.1109/LED.2009.2020442.

- [6] G. Dewey, B. Chu-Kung, J. Boardman, J. M. Fastenau, J. Kavalieros, R. Kotlyar, W. K. Liu, D. Lubyshev, M. Metz, N. Mukherjee, P. Oakey, R. Pillarisetty, M. Radosavljevic, H. W. Then and R. Chau, "Fabrication, Characterization, and Physics of III–V Heterojunction Tunneling Field Effect Transistors (H-TFET) for Steep Sub-threshold Swing," in *IEDM Tech. Dig.*, Washington, DC, USA, Dec. 2011, pp. 33.6.1-33.6.4, DOI: 10.1109/IEDM.2011.6131666.

- [7] E. Memišević, J. Svensson, M. Hellenbrand, E. Lind and L.-E. Wernersson, "Scaling of Vertical InAs–GaSb Nanowire Tunneling Field-Effect Transistors on Si," *IEEE Electron Device Lett.*, vol. 37, no. 5, pp. 549–552, May 2016, DOI: 10.1109/LED.2016.2545861.

- [8] E. Memisevic, J. Svensson, M. Hellenbrand, E. Lind and L.-E. Wernersson, "Vertical InAs/GaAsSb/GaSb Tunneling Field-Effect Transistor on Si with S = 48 mV/decade and  $I_{on} = 10~\mu A/\mu m$  for  $I_{off} = 1~nA/\mu m$  at  $V_{ds} = 0.3~V$ ," in *IEDM Tech. Dig.*, San Francisco, California, USA, Dec. 2016, pp. 19.1.1-19.1.4, DOI: 10.1109/IEDM.2016.7838450.

- [9] J. A. del Alamo, "Nanometer-scale Electronics with III–V Compound Semiconductors," *Nature*, vol. 479, no. 7373, pp. 317-323, Nov. 2011, DOI: 10.1038/nature10677.

- [10] U. E. Avci, D. H. Morris, S. Hasan, R. Kotlyar, R. Kim, R. Rios, D. E. Nikonov and I. A. Young, "Energy Efficiency Comparison of Nanowire Heterojunction TFET and Si MOSFET at Lg = 13 nm, Including P-TFET and Variation Considerations," in *IEDM Tech. Dig.*, Washington, DC, USA, Dec. 2013, pp. 33.4.1–33.4.4, DOI: 10.1109/IEDM.2013.6724744.

- [11] U. E. Avci, D. H. Morris and I. A. Young, "Tunnel Field-Effect Transistors: Prospects and Challenges," *IEEE J. Electron Devices Soc.*, vol. 3, no. 3, pp. 88-95, May 2015, DOI: 10.1109/JEDS.2015.2390591.

- [12] A. Krishnaraja, J. Svensson, E. Memisevic, Z. Zhu, A. R. Persson, E. Lind, L. R. Wallenberg and L.-E. Wernersson, "Tuning of Source Material for InAs/InGaAsSb/GaSb Application-Specific Vertical Nanowire Tunnel FETs," ACS Appl. Electron. Mater., vol. 2, no. 9, pp. 2882-2887, Sep. 2020, DOI: 10.1021/acsaelm.0c00521.

- [13] C. Convertino, C. B. Zota, H. Schmid, D. Caimi, L. Czornomaz, A. M. Ionescu and K. E. Moselund, "A hybrid III–V tunnel FET and MOSFET technology platform integrated on silicon," *Nature Electron.*, vol. 4, no. 2, pp. 162-170, Feb. 2021, DOI: 10.1038/s41928-020-00531-3.

- [14] S. El Kazzi, A. Alian, B. Hsu, A.S. Verhulst, A. Walke, P. Favia, B. Douhard, W. Lu, J.A. del Alamo, N. Collaert and C. Merckling, "Careful stoichiometry monitoring and doping control during the tunneling interface growth of an n + InAs(Si)/p + GaSb(Si) Esaki diode," *J. Crys. Growth*, vol. 484, pp. 86-91, Feb. 2018, DOI: 10.1016/j.jcrysgro.2017.12.035.

- [15] D. Yakimets, G. Eneman, P. Schuddinck, T. H. Bao, M. G. Bardon, P. Raghavan, A. Veloso, N. Collaert, A. Mercha, D. Verkest, A. V. -Y. Thean and K. De Meyer, "Vertical GAAFETs for the Ultimate CMOS Scaling," *IEEE Trans. Electron Devices*, vol. 62, no. 5, pp. 1433-1439, May 2015, doi: 10.1109/TED.2015.2414924.

- [16] K. J. Kuhn, "Considerations for Ultimate CMOS Scaling," *IEEE Trans. Electron Devices*, vol. 59, no. 7, pp. 1813-1828, Jul. 2012, DOI: 10.1109/TED.2012.2193129.

[17] E. Memisevic, J. Svensson, E. Lind and L. Wernersson, "Vertical Nanowire TFETs With Channel Diameter Down to 10 nm and Point S<sub>MIN</sub> of 35 mV/Decade," *IEEE Electron Device Lett.*, vol. 39, no. 7, pp. 1089-1091, Jul. 2018, DOI: 10.1109/LED.2018.2836862.

- [18] B. M. Borg, M. Ek, B. Ganjipour, A. W. Dey, K. A. Dick, L.-E. Wernersson and C. Thelander, "Influence of doping on the electronic transport in GaSb/InAs(Sb) nanowire tunnel devices," *Appl. Phys. Lett.*, vol. 101, no. 4, p. 043508, May 2012, DOI: 10.1063/1.4739082.

- [19] D. Cutaia, K. E. Moselund, H. Schmid, M. Borg, A. Olziersky and H. Riel, "Complementary III–V Heterojunction Lateral NW Tunnel FET Technology on Si," in *Proc. IEEE Symp. VLSI Technol.*, Honolulu, HI, USA, Jun. 2016, pp. 1-2, DOI: 10.1109/VLSIT.2016.7573444.

- [20] Y. Shao, M. Pala, D. Esseni and J. A. del Alamo, "Sub-10-nm Diameter GaSb/InAs Vertical Nanowire Esaki Diodes with Ideal Scaling Behavior: Experiments and Simulations," to be presented at *IEDM*, San Francisco, California, USA, Dec. 2021.

- [21] X. Zhao and J. A. del Alamo, "Nanometer-Scale Vertical-Sidewall Reactive Ion Etching of InGaAs for 3-D III-V MOSFETs," *IEEE Electron Device Lett.*, vol. 35, no. 5, pp. 521-523, May 2014, DOI: 10.1109/LED.2014.2313332.

- [22] W. Lu, X. Zhao, D. Choi, S. El Kazzi and J. A. del Alamo, "Alcohol-Based Digital Etch for III–V Vertical Nanowires with Sub-10 nm Diameter," *IEEE Electron Device Lett.*, vol. 38, no. 5, pp. 548-551, May 2017, DOI: 10.1109/LED.2017.2690598.

- [23] W. Lu, I. P. Roh, D.-M. Geum, S.-H. Kim, J. D. Song, L. Kong and J. A. del Alamo, "10-nm Fin-Width InGaSb p-Channel Self-Aligned FinFETs Using Antimonide-Compatible Digital Etch," in *IEDM Tech. Dig.*, San Francisco, California, USA, Dec. 2017, pp. 17.7.1-17.7.4, DOI: 10.1109/IEDM.2017.8268412.

- [24] A. G. Chynoweth, W. L. Feldmann and R. A. Logan, "Excess Tunnel Current in Silicon Esaki Junctions," *Phys. Rev.*, vol. 121, no. 3, pp. 684-694, Feb. 1961, DOI: 10.1103/PhysRev.121.684.

- [25] J. A. del Alamo, Integrated Microelectronic Devices: Physics and Modeling. 1st ed., New York, NY, USA: Pearson, 2017, pp. 281-348.

- [26] K. Sumita, K. Kato, J. Takeyasu, K. Toprasertpong, M. Takenaka and S. Takagi, "Accurate evaluation of specific contact resistivity between InAs/Ni–InAs alloy using a multi-sidewall transmission line method", *Jpn. J. Appl. Phys.*, vol. 59, no. SG, p. SGGA08, Feb. 2020, DOI: 10.35848/1347-4065/ab6cb3.

- [27] G. Stollwerck, O. V. Sulima and A. W. Bett, "Characterization and simulation of GaSb device-related properties," *IEEE Trans. Electron Devices*, vol. 47, no. 2, pp. 448-457, Feb. 2000, DOI: 10.1109/16.822293.

- [28] M. Berg, J. Svensson, E. Lind and L.-E. Wernersson, "A transmission line method for evaluation of vertical InAs nanowire contacts," *Appl. Phys. Lett.*, vol. 107, no. 23, p. 232102, Dec. 2015, DOI: 10.1063/1.4937125.

- [29] T. B. Bahder, "Eight-band k·p model of strained zinc-blende crystals," Phys. Rev. B, vol. 41, pp. 11992–12001, Jun. 1990, DOI: 10.1103/PhysRevB.41.11992.

- [30] S. Brocard, M. Pala and D. Esseni, "Large on-current enhancement in hetero-junction tunnel-FETs via molar fraction grading," *IEEE Electron Device Lett.*, vol. 35, no. 2, pp. 184–186, Feb. 2014, DOI: 10.1109/LED.2013.2295884.

- [31] I. Vurgaftman, J. R. Meyer, "Band parameters for III–V compound semiconductors and their alloys," *J. Appl. Phys.*, vol. 89, no. 11, pp. 5815–5875, Jun. 2001, DOI: 10.1063/1.1368156.

- [32] S. C. Jain, J. M. McGregor, and D. J. Roulston. "Band-gap narrowing in novel III-V semiconductors," *J. Appl. Phys.*, vol. 68, no. 7, pp. 3747-3749, Jun. 1990, DOI: 10.1063/1.346291.

- [33] G. Stollwerck, O. V. Sulima and A. W. Bett, "Characterization and simulation of GaSb device-related properties," *IEEE Trans. Electron Devices*, vol. 47, no. 2, pp. 448-457, Feb. 2000, DOI: 10.1109/16.822293.

- [34] F. Conzatti, M. Pala, D. Esseni, E. Bano and L. Selmi, "Strain-induced performance improvements in InAs nanowire tunnel FETs," *IEEE Trans. Electron Devices*, vol. 59, no. 8, pp. 2085–2092, Aug. 2012, DOI: 10.1109/TED.2012.2200253.

- [35] A. Cresti, M. G. Pala, S. Poli, M. Mouis and G. Ghibaudo, "A comparative study of surface-roughness-induced variability in silicon nanowire and double-gate FETs," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2274–2281, Aug. 2011. DOI: 10.1109/TED.2011.2147318.

- [36] L. W. Guo, W. Lu, B. R. Bennett, J. B. Boos and J. A. del Alamo, "Ultralow Resistance Ohmic Contacts for p-Channel InGaSb Field-Effect Transistors," *IEEE Electron Device Lett.*, vol. 36, no. 6, pp. 546-548, Jun. 2015, DOI: 10.1109/LED.2015.2421337.